Delamination Risk in Multilayer PCB

By:PCBBUY 01/23/2026 17:28

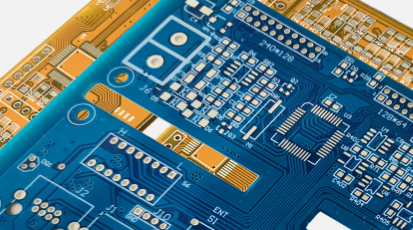

Delamination risk in multilayer PCB is one of the most critical reliability concerns in PCB manufacturing. Delamination refers to the separation between layers within a PCB structure, which can severely impact mechanical strength, electrical performance, and long-term product reliability.

As multilayer PCB designs become thicker, denser, and more thermally demanding, controlling delamination risk has become a key indicator of a manufacturer’s material selection expertise and lamination process capability.

What Is Delamination in Multilayer PCB?

Delamination occurs when bonding between layers—such as copper, prepreg, and core materials—fails partially or completely. It commonly appears as:

-

Separation between resin and copper

-

Layer-to-layer separation inside the laminate

-

Voids or cracks near vias and pads

Unlike surface defects, delamination is often internal and difficult to detect until reliability issues occur.

Common Causes of Delamination Risk in Multilayer PCB

Several factors contribute to delamination:

Poor Resin Flow and Incomplete Bonding

Insufficient resin flow during lamination can prevent proper bonding between layers, especially in high copper density areas.

Material Incompatibility

Mismatch in coefficient of thermal expansion (CTE) between copper and laminate materials creates mechanical stress during thermal cycling.

Excessive Thermal Stress

Repeated exposure to high temperatures during soldering or operation increases the risk of bond failure.

Moisture Absorption

Moisture trapped inside the laminate can expand rapidly during reflow, leading to internal separation.

Material-Related Factors Affecting Delamination

Material selection plays a major role in controlling delamination risk:

-

Resin system compatibility between core and prepreg

-

Glass transition temperature (Tg) suitable for application thermal profiles

-

Resin content and flow characteristics

-

Copper surface treatment quality to improve adhesion

Low-quality or mismatched materials significantly increase delamination risk.

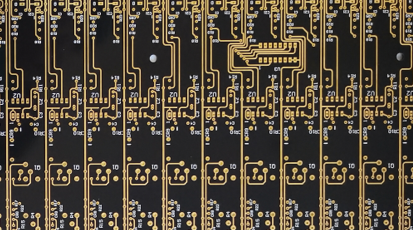

Manufacturing Process Challenges

Delamination is often linked to process control issues:

-

Improper lamination temperature or pressure profiles

-

Resin starvation caused by uneven copper distribution

-

Stackup imbalance leading to mechanical stress

-

Inadequate inner layer surface preparation

Multilayer PCB lamination requires precise coordination of materials and parameters.

Delamination Risk During Assembly and Operation

Even if a PCB passes initial inspection, delamination may still occur during later stages:

-

Lead-free reflow soldering

-

Multiple reflow cycles

-

Long-term thermal cycling in field operation

Boards with marginal lamination quality are especially vulnerable under these conditions.

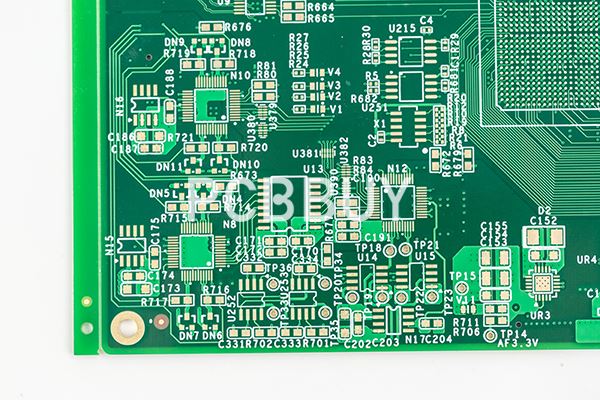

Inspection and Detection of Delamination

Manufacturers use various methods to identify delamination risk:

-

Cross-section analysis to inspect bonding interfaces

-

Acoustic or ultrasonic inspection for internal separation

-

Thermal stress testing to expose latent defects

Early detection helps prevent field failures.

Manufacturing Techniques to Reduce Delamination Risk

Experienced PCB manufacturers apply several techniques to minimize delamination:

-

Optimized prepreg selection based on copper density

-

Balanced stackup and copper distribution

-

Controlled lamination temperature, pressure, and dwell time

-

Moisture control and baking before assembly

These practices significantly improve multilayer PCB reliability.

Design Guidelines to Minimize Delamination

Design choices also influence delamination risk

-

Use symmetrical and balanced stackups

-

Avoid abrupt changes in copper density

-

Design vias and pads to reduce stress concentration

-

Communicate thermal and reliability requirements early

Close cooperation between designers and manufacturers is essential.

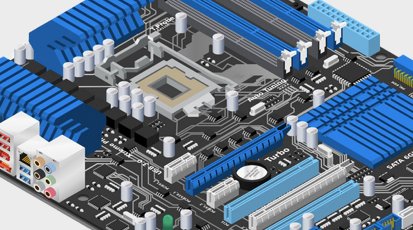

Manufacturing Capability to Control Delamination Risk

Controlling delamination risk in multilayer PCB requires:

-

Qualified laminate and prepreg material systems

-

Advanced lamination presses with stable process control

-

Engineering review of stackup and copper balance

-

Consistent inspection and reliability testing

These capabilities reflect a manufacturer’s experience in producing high-reliability multilayer PCBs.

Typical Applications Requiring Low Delamination Risk

Low delamination risk is critical in:

-

Industrial control electronics

-

Communication and networking equipment

-

Power electronics

-

Automotive and high-reliability systems

In these applications, internal PCB integrity directly affects system stability.

Conclusion

Delamination risk in multilayer PCB manufacturing is influenced by material selection, stackup design, lamination control, and thermal management. Effective prevention requires both engineering expertise and strict process discipline.

Manufacturers with strong lamination and material control capability can consistently deliver multilayer PCBs with high structural integrity and long-term reliability.

FAQ:

What causes delamination in multilayer PCB?

Delamination is mainly caused by poor resin bonding, material incompatibility, thermal stress, moisture absorption, and improper lamination parameters.

Does high layer count increase delamination risk?

Yes. Higher layer count PCBs experience greater internal stress, making precise lamination and material control more critical.

How does moisture affect delamination?

Moisture trapped inside the PCB can expand rapidly during soldering, causing internal separation between layers.

Can delamination be detected during manufacturing?

Yes. Cross-section analysis, acoustic inspection, and thermal stress testing are commonly used to detect delamination risks.

How can delamination risk be reduced?

Delamination risk can be reduced through proper prepreg selection, balanced stackup design, controlled lamination processes, and moisture management.

Industry Category