High Layer Count PCB Yield Improvement Methods

By:PCBBUY 03/27/2026 15:23

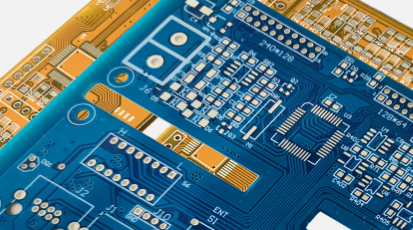

High layer count PCBs (typically 12 layers and above) are widely used in servers, telecommunications, industrial control, automotive electronics, and high-speed digital systems. However, as the number of layers increases, manufacturing complexity rises sharply, making yield control a critical indicator of a PCB factory’s technical capability.

This article introduces proven high layer count PCB yield improvement methods, explaining how advanced manufacturers improve reliability, consistency, and production yield through process control and engineering expertise.

Key Yield Challenges in High Layer Count PCB Manufacturing

|

Challenge Area |

Description |

Impact on Yield |

|

Layer Alignment |

Misregistration during lamination |

Inner layer shorts / opens |

|

Via Reliability |

Aspect ratio increases with thickness |

Barrel cracks, poor plating |

|

Resin Flow Control |

Uneven resin distribution |

Delamination, voids |

|

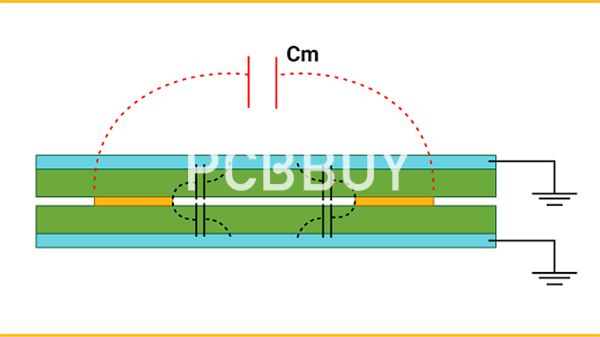

Signal Integrity |

Tight impedance tolerance |

Electrical test failures |

|

Thermal Stress |

Multiple lamination cycles |

Warpage, microcracks |

High Layer Count PCB Yield Improvement Methods (Process-Level Analysis)

1. Inner Layer Fabrication Control

|

Method |

Technical Approach |

Yield Benefit |

|

High-precision imaging |

LDI exposure with fine registration |

Reduces inner layer misalignment |

|

AOI before lamination |

100% inner layer defect detection |

Prevents defect carryover |

|

Etching uniformity control |

Automatic chemistry monitoring |

Stable line width & spacing |

2. Advanced Lamination Process Management

|

Method |

Technical Approach |

Yield Benefit |

|

Multi-stage lamination |

Controlled press cycles by layer group |

Reduces thermal stress |

|

Resin flow simulation |

Prepreg selection by layer density |

Prevents resin starvation |

|

X-ray registration |

Post-lamination alignment verification |

Improves layer accuracy |

3. High Aspect Ratio Via Reliability Improvement

|

Method |

Technical Approach |

Yield Benefit |

|

Optimized drilling parameters |

Controlled spindle speed & feed |

Clean hole walls |

|

Desmear process optimization |

Plasma + wet desmear |

Better copper adhesion |

|

Thick copper via plating |

Pulse plating technology |

Improves via fatigue life |

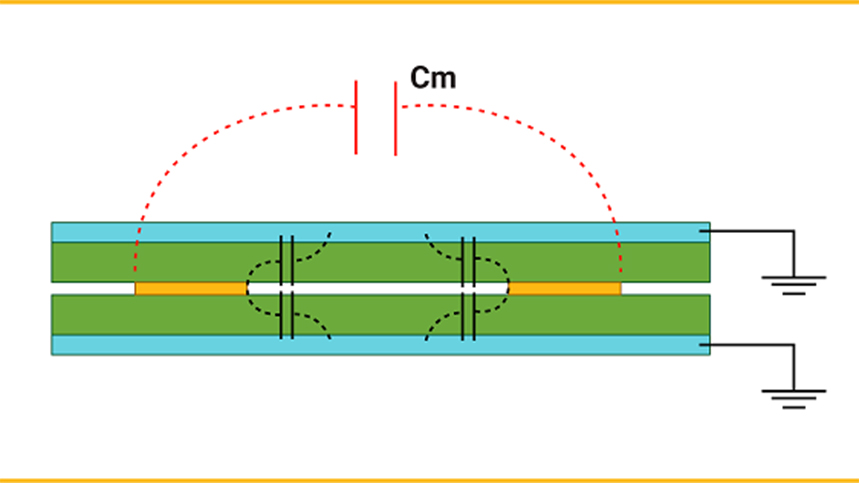

4. Impedance & Signal Integrity Assurance

|

Method |

Technical Approach |

Yield Benefit |

|

Stack-up simulation |

Field solver-based modeling |

First-pass impedance success |

|

Controlled dielectric materials |

Low Dk/Df prepregs & cores |

Stable high-speed performance |

|

Coupon-based testing |

Embedded impedance coupons |

Reduces rework rate |

5. Comprehensive Inspection & Testing Strategy

|

Method |

Technical Approach |

Yield Benefit |

|

AOI at multiple stages |

Inner & outer layer AOI |

Early defect isolation |

|

Flying probe / fixture E-test |

100% electrical testing |

Eliminates latent defects |

|

Microsection analysis |

Statistical cross-sectioning |

Process stability validation |

Why Yield Improvement Reflects a PCB Manufacturer’s Capability

For high layer count PCBs, yield improvement is not a single process, but the result of:

-

Deep understanding of multilayer stack-up design

-

Tight control of lamination and via processes

-

Data-driven SPC and continuous improvement

-

Engineering support from DFM to mass production

Manufacturers with strong yield performance can deliver shorter lead times, lower total cost, and higher long-term reliability.

FAQ

FAQ 1: What is considered a high layer count PCB?

A high layer count PCB typically refers to boards with 12 layers or more, especially those exceeding 16, 20, or 24 layers, where manufacturing complexity increases significantly.

FAQ 2: Why does PCB yield decrease as layer count increases?

As layer count increases, challenges such as layer misalignment, via reliability, resin flow control, and thermal stress become more difficult to manage, increasing the risk of defects.

FAQ 3: What are the most effective high layer count PCB yield improvement methods?

Key methods include precise inner layer AOI, controlled multi-stage lamination, high-aspect-ratio via plating optimization, impedance-controlled stack-up design, and full-process inspection.

FAQ 4: How does lamination affect multilayer PCB yield?

Lamination determines layer alignment, resin distribution, and structural integrity. Poor lamination control can lead to delamination, warpage, and internal shorts.

FAQ 5: Can yield improvement reduce PCB manufacturing cost?

Yes. Higher yield directly reduces scrap, rework, and delivery delays, resulting in lower total manufacturing cost and more stable supply for customers.

FAQ 6: How can customers evaluate a PCB supplier’s yield capability?

Customers can assess yield capability by reviewing:

-

Maximum supported layer count

-

Via aspect ratio limits

-

Impedance tolerance capability

-

Inspection and test coverage

-

Engineering support during DFM

Conclusion

Implementing systematic high layer count PCB yield improvement methods is a key sign of a mature and capable PCB manufacturer. From inner layer processing to final electrical testing, every controlled step contributes to higher reliability and consistent quality—especially for demanding multilayer PCB applications.

Industry Category