How to Calculate Density Error with PCB Layout Guidelines?

By:PCBBUY 04/20/2022 10:13

Many issues are bound to emerge from the lack of accurate or efficient PCB layout preparation. A bigger problem that is probable to arise from a lack of PCB layout preparation is total board failure. Board failure comes in as the most significant issue that arises from poor planning or a lack of PCBs layout preparation reported by many individuals.

Do you know the errors of PCB layout? If you are searching for more information about errors of PCB layout, please check and read the content in this passage.

What are the considerations of high-density PCB design?

As the demand for smaller electronic devices escalates, the printed circuit boards that drive them have had to shrink along with them in order to fit in the box. At the same time, electronics have had to respond to the call for increased capabilities by adding more components and circuitry to the board. To further complicate the problem, PCB component sizes keep decreasing while their pin-counts grow in number, forcing the use of smaller pins with tighter pitches. For the PCB designer, the bag kept getting smaller while everything that went into the bag got larger, and soon the traditional methods of circuit board design had reached their limits.

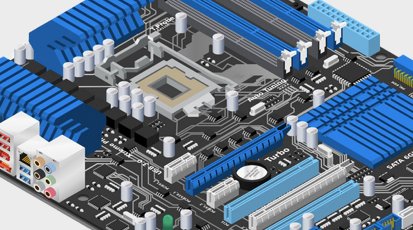

In order to accommodate the need for increased circuitry on smaller board sizes, a new method of PCB design was introduced known as high density interconnect, or HDI. These designs make use of newer fabrication techniques to build boards with smaller line widths and thinner materials, as well as blind and buried vias or laser-drilled microvias. Together these high-density characteristics enable more circuitry to be manufactured in a smaller area of the board and provide a viable connection solution for large pin-count ICs.

The use of these high-density vias also yields a couple of other benefits:

Routing channels: Since blind and buried vias as well as microvias do not go all the way through the board layer stackup, this opens up additional routing channels in the design. Through the strategic placement of these different vias, the designer can now route out of parts that have hundreds of pins on them. Components with this many pins would normally choke off all the inner layer routing channels if only the standard thru-hole vias were used.

Signal integrity: Many of the signals on these devices also have specific signal integrity requirements that can be jeopardized by the full length of a thru-hole via barrel. These vias can act as antennas radiating EMI, or affect the signal return path of a critical net. Using blind and buried vias, or microvias however, eliminates the signal integrity problems that could be caused by the extra length of a thru-hole via.

How to process PCB density errors?

Mixed signal PCBs are another natural environment where the RF circuits go on one side and DSP resides on the other. There may be cases where you’d attach the relevant ground pins to one ground layer but not the one on the far side of the board. This is tricky in a through-hole PCB.

Say it’s a six-layer board with full ground on layers two and five along with flood over the outer layers. I would make one via with a square pad on layers 1 & 2 and another with a square pad on layer 5 & 6. Fanning out the top with square pads on layers 5 & 6 selected and the bottom with the other type leaves a visual cue for which via pads would need a void on the respective ground planes. You may be able to take advantage of other systematic tricks to solve this kind of dilemma on your board.

Circling back to the skill of estimating the technological requirements of a PCB without the benefit of hindsight gained from doing a previous iteration, I’ve compiled a short list of things to watch for.

Placement density factors include:

· Component pitch of the processor and peripherals.

· The size of the regulator circuits - and how many are used.

· Shields and heat-pipes and other large non-electrical hardware

· Significant component keep-out or head-room restrictions.

· Sensors and antennas that require extra space and/or claim all of the layers below.

· The general nature of the board; what does it do?

· The IPC class; high reliability uses larger footprints.

· Underfill, rework, or other assembly process novelties

If the components can be placed on the board without breaking the component spacing rules, then it can be routed. Reducing part size or count may be possible. Look for zero-ohm jumpers that might be replaced with an exacto knife and a jumper wire. Off-boarding the fiducials and tooling holes to the break-off areas of the assembly sub-panel may buy you additional room. Reducing the silkscreen to deprioritize reference designators and then part outlines may help but try to keep polarity marks as a last resort.

Industry Category