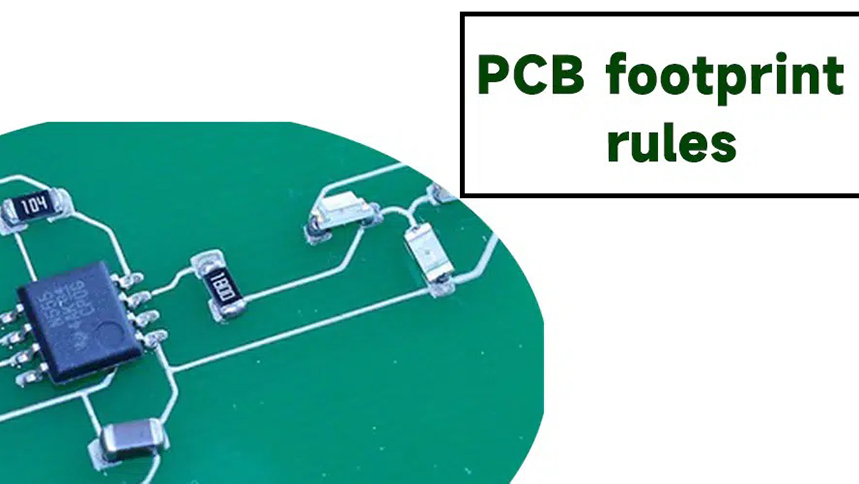

How to Process PCB Footprint Design: A Comprehensive Guide for Engineers

By:PCBBUY 05/28/2025 15:38

Introduction: The Foundation of Reliable Electronics

PCB footprint design is a critical step in the development of electronic assemblies, directly impacting electrical performance, manufacturing yield, and long-term reliability. A properly designed footprint ensures optimal mechanical stability, solder joint integrity, and signal integrity. This guide provides a systematic approach to footprint design, supported by industry standards, material science, and practical engineering principles.

1. Understanding PCB Footprint Design

1.1 Definition and Purpose

A PCB footprint (or "land pattern") defines the geometric outline and pad layout for a specific electronic component (e.g., resistors, ICs, connectors). Its core functions include:

-

Mechanical Support: Aligning the component during placement.

-

Electrical Conduction: Providing low-resistance paths for signals and power.

-

Thermal Management: Ensuring proper solder flow and heat dissipation.

1.2 Key Design Principles

|

Parameter |

Design Objective |

|

Pad Size |

Match component terminal size (±10% tolerance for SMD components). |

|

Pad Spacing |

Avoid short circuits; follow IPC-7351 guidelines (e.g., ≥0.15mm gap for 0402 parts). |

|

Aperture Ratio |

Balance solder paste retention (≥70% coverage) and stencil cleaning efficiency. |

2. Step-by-Step Design Process

2.1 Data Collection

Component Specifications

-

Extract dimensions, pitch, and terminal shapes from the datasheet. Example:

o QFN package: Requires thermal pads (e.g., exposed pad for heat dissipation).

o BGA: Demands precise ball grid alignment (typically ±0.05mm tolerance).

Manufacturing Constraints

-

PCB Tolerances: Account for typical fabrication limits (e.g., ±0.1mm for etching, ±0.05mm for drilling).

-

Solder Paste Slump: Adjust pad sizes to compensate for slump in high-temperature reflow (e.g., increase pad width by 10%-15%).

2.2 Pad Geometry Design

Pad Shape

-

Rectangular Pads: Standard for SMD components (e.g., 0402, 1206).

-

Circular Pads: Suitable for through-hole components (THT) or radial lead parts.

-

Octagonal/Square Pads: Reduce solder bridging risks (recommended for fine-pitch components like QFP).

Pad Sizing Formula

|

Component Type |

Pad Length (L) |

Pad Width (W) |

|

0402 (Metric) |

0.4mm + (0.05mm ~ 0.1mm) |

0.2mm + (0.03mm ~ 0.08mm) |

|

QFN (4x4mm Body) |

Body size + (0.2mm ~ 0.4mm) |

Thermal pad: Body + 0.1mm |

Example: For a 0402 resistor, pad length = 0.4mm + 0.07mm = 0.47mm.

2.3 Material and Stackup Considerations

Substrate Material

-

FR-4: Standard for consumer electronics (dielectric constant ε=4.3~4.8).

-

High-Tg Laminates: Required for automotive or industrial applications (thermal resistance up to 180°C).

Copper Weight

-

1 oz/ft² (35 μm): Suitable for low-current signals.

-

2 oz/ft² (70 μm): Recommended for power planes or high-current traces.

3. Advanced Design Considerations

3.1 Thermal and Mechanical Stress Mitigation

-

Coefficient of Thermal Expansion (CTE) Matching: Align PCB material (e.g., FR-4 CTE = 13-17 ppm/°C) with component CTE (e.g., ceramic ICs: ~7 ppm/°C). Use solder mask or flexible adhesives to buffer mismatch stresses.

-

Solder Joint Relief: Non-solder regions (e.g., component body) must have ≥0.1mm clearance from solder pads to prevent reflow defects.

3.2 Electrical Performance Optimization

Impedance Control

-

For high-speed signals (e.g., DDR, HDMI), use controlled impedance footprints:

o Microstrip: Z₀ = [87 / (ε⁺)] × ln(5.98h/w) (h = dielectric height, w = trace width).

o Differential Pairs: Maintain tight spacing (e.g., 0.1mm gap) to preserve coupling capacitance.

Ground Plane Integration

-

Antipads: Clearance holes in ground planes to avoid parasitic capacitance (minimum 0.15mm clearance for <5GHz signals).

4. Design Validation and Testing

4.1 Simulation Tools

-

Ansys Sherlock: For warpage and CTE simulation.

-

SIwave: To verify signal integrity in high-speed footprints.

4.2 Prototype Testing

|

Test Type |

Objective |

|

Solder PasteInspection (SPI) |

Verify pad fill ratio (target: >70% coverage). |

|

Automated Optical Inspection (AOI) |

Check pad alignment and solder joint quality. |

|

X-ray Inspection |

Detect hidden voids (acceptance threshold: <25% of joint area). |

5. Common Pitfalls and Best Practices

5.1 Avoidable Mistakes

-

Oversized Pads: Cause solder bridging (e.g., 0.5mm gap for 0.4mm pitch BGA is risky).

-

Inadequate Solder Mask Slap: Leaves pad edges exposed to oxidation (maintain ≥0.05mm margin).

5.2 Industry Best Practices

-

Follow IPC-2221/2222 standards for through-hole components.

-

Use kinematic fixtures in footprint libraries to simplify alignment.

6. Material and Process Recommendations

|

Parameter |

Recommendation |

|

Surface Finish |

ENIG (Electroless Ni/Au) for high-reliability applications (Shelf life: >24 months). |

|

Solder Paste Particle |

Type 4 (25–45μm) for 0402+ components; Type 5 (15–25μm) for ultra-fine pitch. |

|

Reflow Profile |

Peak temperature: 245°C ±5°C; Time above liquidus: 60–90 seconds. |

Conclusion

Mastering PCB footprint design requires a blend of mechanical precision, electrical engineering, and material science. By adhering to IPC standards, leveraging simulation tools, and validating designs through rigorous testing, engineers can minimize errors and enhance product robustness. Continuous collaboration between design teams and manufacturers remains key to optimizing footprints for specific applications.

References

-

IPC-7351, Generic Library of Footprints.

-

JEDEC Standards (e.g., MO-221 for SOT packages).

-

"Solder Paste Reflow Process" by Clyde Coombs (IEEE Press, 2020).

-

ANSYS Sherlock User Manual (ANSYS Inc., 2023).

Industry Category