Lamination Void Prevention in Multilayer PCB

By:PCBBUY 03/26/2026 14:50

In multilayer PCB manufacturing, lamination voids are one of the most critical defects affecting mechanical strength, electrical reliability, and long-term performance.

Effective lamination void prevention in multilayer PCB production requires precise control of materials, lamination parameters, and process consistency.

At PCBBUY, void prevention is a core part of multilayer PCB process engineering, especially for high layer count, HDI, and high-reliability applications.

What Are Lamination Voids in Multilayer PCBs?

Lamination voids are air pockets or unfilled areas trapped between PCB layers during the lamination process. These voids weaken interlayer bonding and may lead to reliability failures.

|

Void Type |

Description |

|

Resin Starvation Voids |

Insufficient resin flow between layers |

|

Air Entrapment Voids |

Trapped air during heating and pressure |

|

Micro-voids |

Small voids around copper features |

|

Interface Voids |

Poor bonding between core and prepreg |

Why Lamination Void Prevention Is Critical

|

Impact Area |

Potential Risk |

|

Mechanical Strength |

Reduced layer adhesion, delamination |

|

Electrical Performance |

Impedance instability, signal loss |

|

Thermal Reliability |

Increased risk of cracking under thermal stress |

|

Long-Term Reliability |

Higher failure rates in harsh environments |

Void prevention is especially important in multilayer PCBs with dense copper patterns and complex stack-ups.

Common Causes of Lamination Voids in Multilayer PCBs

|

Cause Category |

Description |

|

Prepreg Resin Flow |

Inadequate or inconsistent resin flow |

|

Lamination Profile |

Incorrect temperature, pressure, or time |

|

Copper Distribution |

Uneven copper density blocking resin flow |

|

Moisture Content |

Moisture trapped in materials |

|

Stack-up Design |

Poor gap design between inner layers |

Understanding these root causes is the foundation of effective void prevention.

Lamination Void Prevention Methods at PCBBUY

|

Process Area |

PCBBUY Control Method |

|

Material Selection |

Qualified prepreg with controlled resin flow |

|

Resin Flow Evaluation |

Prepreg resin flow testing before production |

|

Stack-up Engineering |

Optimized copper balance and layer spacing |

|

Lamination Profile |

Precisely controlled temperature & pressure ramps |

|

Vacuum Lamination |

Air removal before and during lamination |

|

Moisture Control |

Pre-baking of cores and prepregs |

|

Process Monitoring |

Real-time process parameter tracking |

These measures ensure complete resin filling and strong interlayer bonding.

Lamination Process Control for Multilayer PCBs

|

Lamination Stage |

Key Control Focus |

|

Pre-lamination |

Material baking and moisture removal |

|

Vacuum Stage |

Efficient air evacuation |

|

Heating Ramp |

Controlled resin softening and flow |

|

Pressure Application |

Uniform pressure across panel |

|

Cure & Cooling |

Stable curing to avoid internal stress |

Each stage plays a direct role in lamination void prevention.

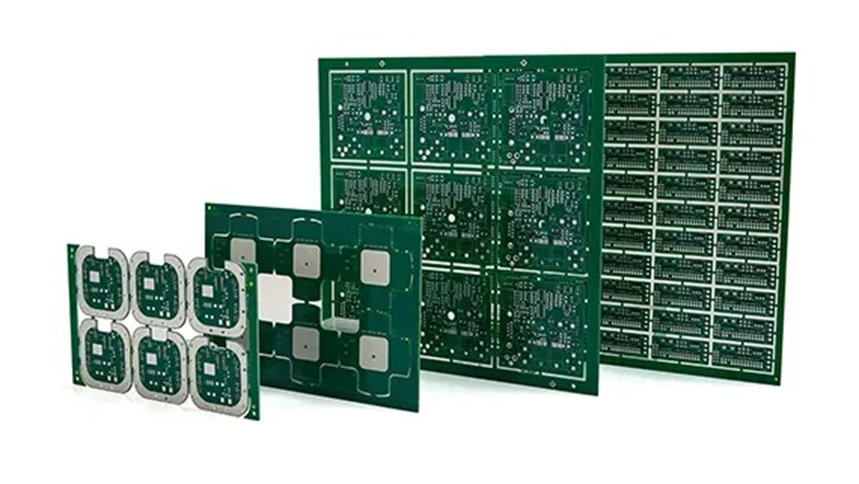

PCB Types Requiring Strict Void Prevention

|

PCB Type |

Reason |

|

High Layer Count PCBs |

Increased lamination interfaces |

|

HDI PCBs |

Fine structures sensitive to voids |

|

Impedance-Controlled PCBs |

Dielectric consistency required |

|

High-Reliability PCBs |

Long-term thermal and mechanical stability |

|

Industrial & Medical PCBs |

High safety and reliability standards |

Quality Inspection & Verification

To ensure effective lamination void prevention, PCBBUY applies multiple inspection methods:

|

Inspection Method |

Purpose |

|

X-ray Inspection |

Detects internal voids |

|

Cross-Section Analysis |

Verifies resin filling and bonding |

|

AOI |

Confirms surface integrity |

|

Reliability Testing |

Thermal and mechanical stress evaluation |

All results are recorded for full traceability.

FAQ

Q1: What causes lamination voids in multilayer PCBs?

Lamination voids are mainly caused by insufficient resin flow, trapped air, improper lamination parameters, uneven copper distribution, or moisture in materials.

Q2: Why is vacuum lamination important for void prevention?

Vacuum lamination removes trapped air before resin flow, significantly reducing the risk of air entrapment voids.

Q3: How does prepreg resin flow affect void formation?

Proper resin flow ensures complete gap filling between layers. Too little resin flow leads to voids, while excessive flow may cause other defects.

Q4: Are lamination voids more common in high layer count PCBs?

Yes. As layer count increases, the number of lamination interfaces rises, making void prevention more challenging.

Q5: How does PCBBUY prevent lamination voids?

PCBBUY combines material qualification, resin flow testing, optimized stack-up design, vacuum lamination, and strict process control to minimize void risks.

Q6: Can lamination voids affect electrical performance?

Yes. Voids can cause impedance variation, signal degradation, and long-term reliability issues, especially in high-speed designs.

Conclusion

Effective lamination void prevention in multilayer PCB manufacturing is essential for achieving strong interlayer bonding, stable electrical performance, and long-term reliability.

Through advanced lamination processes, strict material control, and comprehensive inspection, PCBBUY delivers high-quality multilayer PCB solutions that meet international standards and demanding application requirements.

Industry Category