Lamination Void Prevention in Multilayer PCB

By:PCBBUY 01/30/2026 17:04

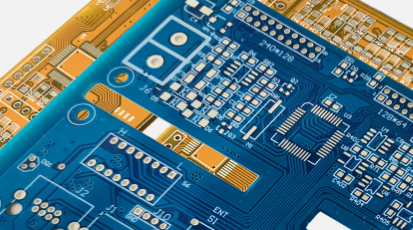

In multilayer PCB manufacturing, lamination quality is one of the most critical factors affecting long-term reliability. Among various lamination-related defects, lamination voids are particularly problematic because they are often hidden inside the board and difficult to detect during routine inspection.

Effective lamination void prevention in multilayer PCB requires a deep understanding of materials, stackup design, and lamination process control. This article explains what lamination voids are, why they occur, and how professional PCB manufacturers prevent them through controlled manufacturing practices.

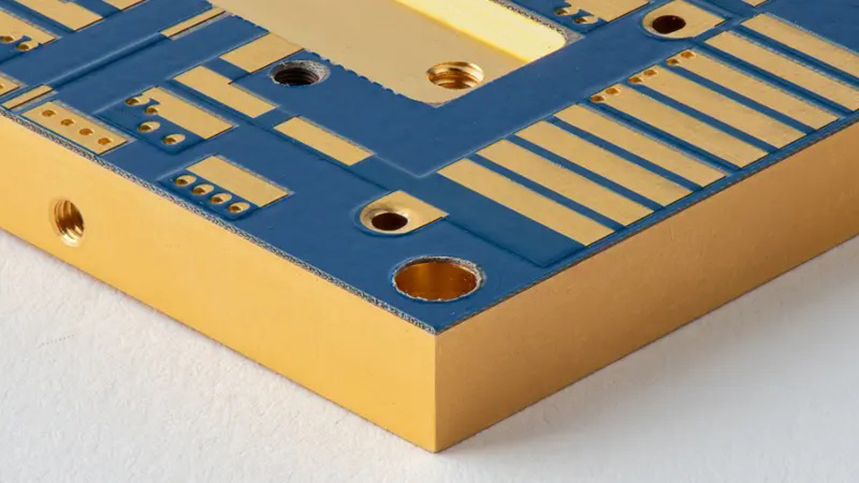

What Are Lamination Voids in Multilayer PCB?

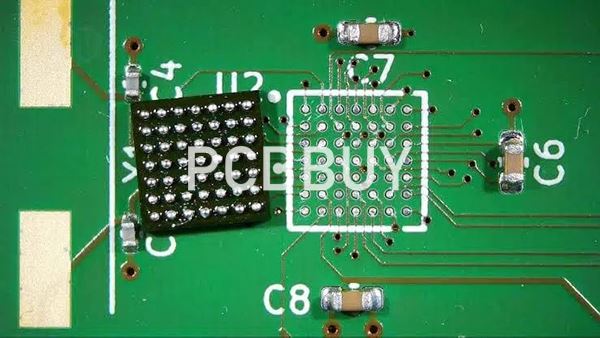

Lamination voids are air pockets or unfilled regions trapped between layers during the lamination process. They typically occur:

-

Between prepreg and copper layers

-

Around dense copper patterns

-

Near vias or resin-poor areas

Voids can range from microscopic defects to large unbonded areas, depending on process conditions and material selection.

Why Lamination Voids Are a Serious Reliability Risk?

Although some lamination voids may not cause immediate electrical failure, they significantly weaken PCB reliability over time.

Key risks include:

-

Reduced interlayer bonding strength

-

Increased susceptibility to delamination

-

Moisture ingress leading to insulation degradation

-

Crack propagation under thermal cycling

In high-reliability applications, even small voids are considered unacceptable.

Common Causes of Lamination Voids

|

Cause |

Description |

Resulting Risk |

|

Trapped air |

Inadequate vacuum or venting |

Void formation |

|

Moisture |

Prepreg or core absorbs humidity |

Gas expansion during heating |

|

Insufficient resin flow |

Resin cannot fully fill gaps |

Weak bonding |

|

Improper press profile |

Incorrect temperature or pressure |

Incomplete curing |

|

Copper imbalance |

Uneven pressure distribution |

Local voids |

These factors often interact, making void prevention a system-level challenge.

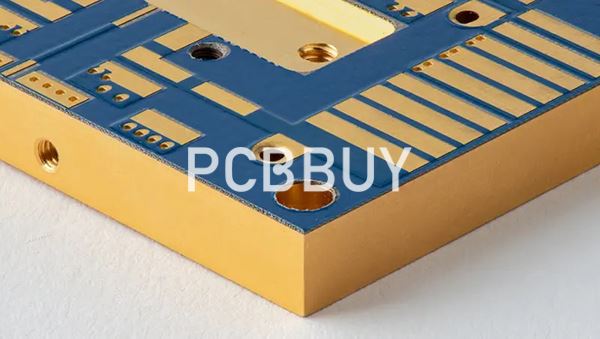

Material Factors Influencing Void Formation

Prepreg Resin Content and Flow

Low resin content or mismatched prepreg flow characteristics can prevent complete filling of copper patterns.

Glass Weave Style

Coarse glass styles may create resin-poor zones, especially in high-density designs.

Moisture Absorption

Improper material storage increases moisture content, which can vaporize during lamination and create voids.

Manufacturers must carefully qualify materials and control storage conditions.

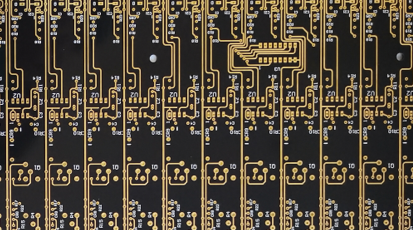

Stackup Design and Its Impact on Void Prevention

Stackup design strongly affects pressure and resin distribution during lamination.

Key considerations include:

-

Symmetrical stackups for even pressure

-

Balanced copper distribution across layers

-

Consistent dielectric thickness

Poor stackup design can force resin away from certain regions, increasing void risk.

Lamination Process Control for Void Prevention

Professional PCB manufacturers implement strict lamination controls, including:

-

Vacuum lamination to remove trapped air

-

Multi-stage temperature ramps to control resin flow

-

Optimized pressure profiles to ensure full contact

-

Controlled curing cycles to stabilize resin cross-linking

These measures ensure that resin fully fills interlayer gaps before curing.

Manufacturing Environment and Process Discipline

Environmental control plays a critical role in void prevention:

-

Pre-baking materials to remove moisture

-

Controlled humidity in lamination areas

-

Proper handling to avoid contamination

Consistent process discipline significantly reduces lamination defects.

Inspection and Detection of Lamination Voids

To verify lamination quality, manufacturers perform:

-

Cross-section analysis

-

Visual inspection of critical areas

-

Thickness uniformity measurement

-

Reliability testing after lamination

These inspections help detect potential void-related risks before shipment.

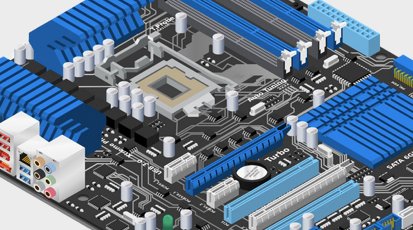

How PCBBUY Prevents Lamination Voids in Multilayer PCB?

PCBBUY applies a systematic approach to lamination void prevention:

-

Qualified prepreg and core material selection

-

Copper balance optimization during panel design

-

Controlled vacuum lamination processes

-

In-process monitoring and post-lamination inspection

This integrated process control ensures stable bonding and long-term reliability in multilayer PCB production.

Design Guidelines to Reduce Lamination Void Risk

Designers can support void prevention by:

-

Avoiding extreme copper density variation

-

Maintaining balanced stackups

-

Coordinating stackup and material selection with the manufacturer

-

Engaging in early DFM review

Close collaboration significantly improves lamination outcomes.

Conclusion

Lamination void prevention in multilayer PCB manufacturing is essential for ensuring mechanical integrity and long-term reliability. Through careful material control, optimized stackup design, and precise lamination process management, experienced manufacturers can effectively eliminate void-related risks.

Choosing a PCB supplier with proven multilayer lamination expertise is a key factor in achieving consistent and reliable PCB quality.

FAQ

What causes lamination voids in multilayer PCB?

Lamination voids are caused by trapped air, moisture, insufficient resin flow, improper lamination profiles, or copper imbalance in the stackup.

How do lamination voids affect PCB reliability?

Voids weaken interlayer bonding and can lead to delamination, insulation failure, and cracking during thermal cycling.

Can lamination voids be detected after manufacturing?

Some voids can be identified through cross-section inspection, but prevention during lamination is more effective than post-process detection.

How do PCB manufacturers prevent lamination voids?

Manufacturers use vacuum lamination, material pre-baking, optimized press cycles, and strict process control to eliminate voids.

Does stackup design influence lamination void formation?

Yes. Stackup symmetry and copper balance strongly affect resin flow and pressure distribution during lamination.

Industry Category